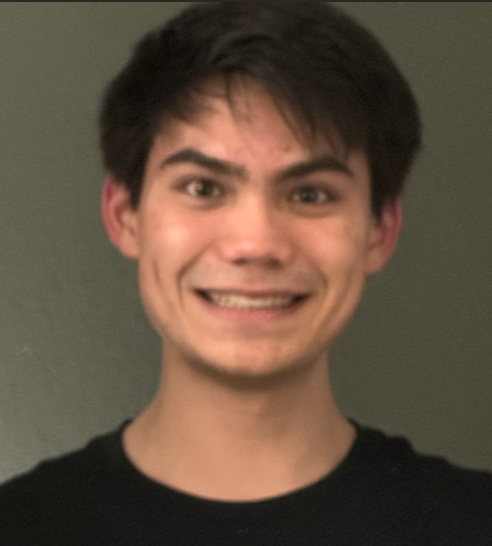

Nicolas Rault-Wang

UC Berkeley Applied Math & CS undergraduate researching computational imaging, machine learning for scientific instrumentation, and large-scale data systems at the Space Sciences Laboratory.

Research Focus

I develop machine learning systems and computational methods for scientific instrumentation, with expertise spanning computer vision, distributed systems, and hardware-software co-design. My research bridges theoretical mathematics with practical implementation to solve challenging problems in astronomical data analysis and real-time transient detection.

Publications & Presentations

Nanosecond differential timing using inexpensive differential GNSS receivers (conference abstract)

B. Godfrey, W. Liu, N. Rault-Wang, J. Kocz, D. Werthimer

2025 United States National Committee of URSI National Radio Science Meeting (USNC-URSI NRSM), Jan. 2025, 431–431.

DOI: 10.23919/USNC-URSINRSM66067.2025.10906985Machine learning applications for anomaly and interference detection on PANOSETI data

N. Rault-Wang, Y. Dong, W. Liu, D. Werthimer, J. Maire, and S. Wright

PANOSETI Collaboration Meeting (Plenary Talk), San Diego, CA, United States, Jan. 2025.

DOI: 10.5281/zenodo.17388495Identifying clouds in panoramic SETI data with machine learning

N. Rault-Wang, et al.

2024 Assembly of the Order of the Octopus (Poster Presentation), Green Bank, WV, United States, Aug. 2024.

DOI 10.5281/zenodo.14590904Research Projects

Deep Learning for PANOSETI

Computer VisionDesigned and implemented the first deep learning pipeline for the PANOSETI collaboration, achieving 95% classification accuracy and 0.97 average precision in automated interference detection for the project’s daily terabyte-scale datasets of wide-field, 20μs-integration optical/near-IR images.

High-speed Data Acquisition System

SystemsDeveloped and maintained an ultra-high data rate (100k frames/sec) C++ acquisition pipeline, integrating an asynchronous gRPC API, leading several extensibility-focused refactors, and establishing a full GitHub Actions CI pipeline to validate fault-tolerance and >99.99% data integrity.

Terabyte-scale Data Pipeline

Distributed SystemsCo-designed and implemented a scalable data reduction pipeline (TensorStore, Zarr, Dask) for terabyte-scale datasets, leading technical prototyping from a self-administered 12TiB BeeGFS cluster to San Diego Supercomputer Center HPC facilities.

Unsupervised Anomaly Detection

Computer VisionProposed and prototyped an unsupervised anomaly detector using a β-Variational Autoencoder, capable of clustering Cherenkov events, noise, and stellar signals based on low-dimensional latent embeddings.

Characterizing Polar Express

OptimizationEmpirically characterized the Polar Express Muon variant, evaluating its sensitivity to key hyperparameters and the extent to which it stablizes the attention mechanism in Transformer architectures.

Education

University of California, Berkeley

Aug 2021 – Dec 2025Bachelor of Arts, double major in Applied Mathematics and Computer Science

GPA: 3.88

Relevant Coursework:

Advanced Coursework and Projects

CS 180: Computer Vision & Computational Photography

The following are write-ups from my CS 180 projects, each of which reproduces results from key papers in computer vision.

Apple-Sponsored CPU Design Contest Winner

Awarded 1st Place (out of 18 two-person teams) in a Spring 2025 Apple-sponsored RISC-V CPU design contest in a team with Neel Gajare.

- We achieved the contest's best PPA (Power, Performance, Area) metrics over the past two years: lowest resource utilization, 1.06 CPI, and 125 MHz clock frequency.

- Led the microarchitecture and engineering workflow (Git feature-branching, regression testing) to design a fully bypassed, 5-stage RISC-V pipeline in Verilog RTL, including speculative execution via a branch target buffer.

- Synthesized the core entirely on the Programmable Logic (PL) fabric of a Xilinx Zynq-7000 (XC7Z020), validating the design with a custom SystemVerilog verification suite.

See my write-up at the link below!

Get In Touch

I'm currently exploring PhD opportunities in computational imaging and machine learning systems. Feel free to reach out if you're interested in collaboration or discussion.